# Hybrid Multi-Level Inverters Implemented in Photovoltaic Systems قلابات الفولتية الهجينية متعددة المستويات في انظمة الطاقة الكهروضوئية

Submitted by:

Fadi Jaber

### Supervised by:

Dr. Muhammad Abu Khaizaran Dr. Mahran Quraan

### Committee

Dr. Muhammad Abu Khaizaran Dr. Mahran Quraan Dr. Hakam Shehadeh Dr. Samer Al Sadi

This Thesis was submitted in partial fulfillment of the requirements for the Master's Degree in Electrical Engineering from the Faculty of Engineering and Technology at Birzeit University, Palestine

January 2021

# Hybrid Multi-Level Inverters Implemented in Photovoltaic Systems قلابات الفولتية الهجينية متعددة المستويات في انظمة الطاقة الكهروضوئية

### Submitted by:

Fadi Jaber

## **Approved by the Examining Committee:**

Dr. Muhammad Abu Khaizaran

Dr. Mahran Quraan

Dr. Hakam Shehadeh

Dr. Samer Al Sadi

January 2021

# **Declaration of Authorship**

I declare that this thesis entitled "Hybrid Multi-Level Inverters Implemented in Photovoltaic Systems" is the result of my own research except as cited in the references. It is being submitted to the Master's Degree in Electrical Engineering from the Faculty of Engineering and Technology at Birzeit University, Palestine. The thesis has not been accepted for any degree and is not concurrently submitted in candidature of any other degree.

Signed:

Date:

## Abstract

This thesis focuses on new Hybrid Multi-Level Inverters and their applications in the Photovoltaic systems. Both voltage and Current Source Inverters were surveyed, studied, some of them were simulated and analyzed using MATLAB/Simulink software. A comparison between the MLIs and HMLIs was conducted at the end of this thesis. Detailed analysis was done on the HMLI focusing on the Asymmetrical H-Bridge topology. It was studied under various environmental factors including irradiance and temperature. Also, the functionality of the control process of the inverter was investigated under variation of the load and different values of reference active power, reactive power and DC-link voltage. The results showed that, the inverter and the adaptive control process succeeded in producing a robust inverter that can be operated in different modes of power injection and had a high immunity against various weather conditions.

المستخلص

تركز هذه الرسالة على القلابات الهجينة متعددة المستويات الجديدة وتطبيقاتها في الأنظمة الكهر وضوئية. لقد تم مسح ودر اسة ومحاكاة وتحليل كل من الجهد وقلاب الجهد المقترح باستخدام برنامجMATLAB\SIMULINK. وقد تم إجراء مقارنة ما بين القلابات الهجينة والقلابات متعددة المستويات في نهاية هذه الرسالة. وقد تم أيضا إجراء تحليل مفصل على HMLI مع التركيز على أساس H-Bridge غير متكافئة مداخل الجهد باعتماد التناظر الثلاثي. أيضا تمت در اسة القلاب الهجين في الرسالة تحت عوامل بيئية مختلفة بما في ذلك الإشعاع ودرجة الحرارة. بالإضافة إلى التحقيق في وظيفة عملية التحكم في القلاب تحت تغير الحمل والقيم المختلفة التي تشير إلى الطاقة الفعالة والقدرة التفاعلية و جهد المدخل الكامل. أوضحت النتائج منابعة عالية التحكم في أساس عليمان المختلفة الذي الإشعاع ودرجة الحرارة. بالإضافة إلى التحقيق في وظيفة عملية التحكم في منابعة تعير الحمل والقيم المختلفة التي تشير إلى الطاقة الفعالة والقدرة التفاعلية و جهد المدخل الكامل. أوضحت النتائج أن القلاب وعملية التحكم المتكيفة قد نجحا في إنتاج قلاب قوي يمكن أن يعمل في أوضاع مختلفة لتزويد الطاقة الشبكة و وله مناعة عالية ضد الظروف الجوية المختلفة.

# **Index Terms**

Hybrid Multi-Level Inverter

PV Grid-Tied Inverters

Grid-Tied Inverters Control Process

LCL Coupling Filters

# **Table of Contents**

| ABSTRACT                                                   |

|------------------------------------------------------------|

| اااالمستخلص                                                |

| INDEX TERMS IV                                             |

| TABLE OF CONTENTSV                                         |

| ACRONYMS AND ABBREVIATIONSVIII                             |

| LIST OF FIGURES IX                                         |

| LIST OF TABLESXI                                           |

| CHAPTER 1. INTRODUCTION1                                   |

| 1.1 Introduction1                                          |

| 1.2 Problem Statements1                                    |

| 1.3 Contribution1                                          |

| 1.4 Research Goals2                                        |

| 1.5 Organization of the Thesis2                            |

| CHAPTER 2. LITERATURE REVIEW                               |

| 2.1 Introduction                                           |

| 2.2 Features of Multi-Level Inverters4                     |

| 2.3 What is Hybrid?5                                       |

| 2.4       Photovoltaic Systems                             |

| CHAPTER 3. MULTI-LEVEL AND HYBRID MULTI-LEVEL INVERTERS 11 |

| 3.1 Voltage Source Inverters (VSIs)                        |

| 3.1.1 Multi-Level Voltage Source Inverters                 |

| 3.1.1                                                                                                                                                                                                                      | .1 Neutral Point Clamped (NPC) Inverter                                                                                                                                                                                                                      | 12                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 3.1.1                                                                                                                                                                                                                      | .2 Cascaded H-Bridge Inverter                                                                                                                                                                                                                                | 13                                                                         |

| 3.1.1                                                                                                                                                                                                                      | .3 Flying Capacitor Multi-Level Inverter                                                                                                                                                                                                                     | 17                                                                         |

| 3.1.2                                                                                                                                                                                                                      | Hybrid Multi-Level Voltage Source Inverter                                                                                                                                                                                                                   |                                                                            |

|                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                              |                                                                            |

| 3.2 C                                                                                                                                                                                                                      | urrent Source Inverters                                                                                                                                                                                                                                      | 20                                                                         |

| 3.2.1                                                                                                                                                                                                                      | PWM Current Source Inverter                                                                                                                                                                                                                                  | 20                                                                         |

| 3.2.2                                                                                                                                                                                                                      | Parallel Current Source Inverters                                                                                                                                                                                                                            | 22                                                                         |

| 3.2.3                                                                                                                                                                                                                      | Load-Commutated Current Source Inverter (LC CSI)                                                                                                                                                                                                             | 23                                                                         |

| 3.2.4                                                                                                                                                                                                                      | Boost-Type CSI                                                                                                                                                                                                                                               |                                                                            |

| 3.2.4                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                              |                                                                            |

| 3.2.4                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                              |                                                                            |

| 0.1=1.1                                                                                                                                                                                                                    | C CSI                                                                                                                                                                                                                                                        |                                                                            |

| 3.2.6                                                                                                                                                                                                                      | Multi-Level Current Source Inverters (MCSIs)                                                                                                                                                                                                                 |                                                                            |

| 3.2.6                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                              |                                                                            |

| 3.2.0                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                              |                                                                            |

|                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                              |                                                                            |

| 3.2.6                                                                                                                                                                                                                      | 6                                                                                                                                                                                                                                                            |                                                                            |

| 3.2.6                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                              |                                                                            |

| 3.2.6                                                                                                                                                                                                                      | 0 0                                                                                                                                                                                                                                                          |                                                                            |

| 3.2.6                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                              |                                                                            |

|                                                                                                                                                                                                                            | .7 Reduced Count Switch Multi-Level CSI                                                                                                                                                                                                                      |                                                                            |

| 3.2.6                                                                                                                                                                                                                      | .8 Parallel Inductor Multi-Level CSI                                                                                                                                                                                                                         | 33                                                                         |

|                                                                                                                                                                                                                            | ER 4. MULTI-LEVEL INVERTERS MODULATION TECHNIQUES                                                                                                                                                                                                            |                                                                            |

| 4.1 Sillus                                                                                                                                                                                                                 | idal Pulse Width Modulation                                                                                                                                                                                                                                  | 34                                                                         |

|                                                                                                                                                                                                                            | Idal Pulse Width Modulation                                                                                                                                                                                                                                  |                                                                            |

| 4.2 Phase                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                              | 37                                                                         |

| 4.2 Phase<br>4.3 Level                                                                                                                                                                                                     | Shifted Multicarrier Modulation                                                                                                                                                                                                                              | 37<br>37                                                                   |

| <ul><li>4.2 Phase</li><li>4.3 Level-</li><li>4.4 Hybri</li></ul>                                                                                                                                                           | Shifted Multicarrier Modulation<br>Shifted Multicarrier Modulation<br>d Multi-Level Inverter Analysis                                                                                                                                                        | 37<br>37<br>38                                                             |

| <ul> <li>4.2 Phase</li> <li>4.3 Level-</li> <li>4.4 Hybri<br/>4.4.1 A</li> </ul>                                                                                                                                           | Shifted Multicarrier Modulation<br>Shifted Multicarrier Modulation<br>d Multi-Level Inverter Analysis<br>symmetrical Hybrid Multi-Level Inverter (AHMLI)                                                                                                     | 37<br>37<br>38<br>38                                                       |

| <ul> <li>4.2 Phase</li> <li>4.3 Level-</li> <li>4.4 Hybri<br/>4.4.1 A</li> </ul>                                                                                                                                           | Shifted Multicarrier Modulation<br>Shifted Multicarrier Modulation<br>d Multi-Level Inverter Analysis                                                                                                                                                        | 37<br>37<br>38<br>38                                                       |

| <ul> <li>4.2 Phase</li> <li>4.3 Level-</li> <li>4.4 Hybri<br/>4.4.1 A<br/>4.4.1</li> </ul>                                                                                                                                 | Shifted Multicarrier Modulation<br>Shifted Multicarrier Modulation<br>d Multi-Level Inverter Analysis<br>symmetrical Hybrid Multi-Level Inverter (AHMLI)                                                                                                     | 37<br>37<br>38<br>38<br>39                                                 |

| <ul> <li>4.2 Phase</li> <li>4.3 Level-</li> <li>4.4 Hybri<br/>4.4.1 A<br/>4.4.1</li> <li>CHAPT</li> </ul>                                                                                                                  | Shifted Multicarrier Modulation<br>Shifted Multicarrier Modulation<br>d Multi-Level Inverter Analysis<br>symmetrical Hybrid Multi-Level Inverter (AHMLI)<br>Asymmetric Trinary Hybrid Multi-Level Inverter (THMLI)<br>ER 5. GRID-TIED PV INVERTERS           | 37<br>37<br>38<br>39<br>43                                                 |

| <ul> <li>4.2 Phase</li> <li>4.3 Level-</li> <li>4.4 Hybri<br/>4.4.1 A<br/>4.4.1</li> <li>CHAPT</li> </ul>                                                                                                                  | Shifted Multicarrier Modulation<br>Shifted Multicarrier Modulation<br>d Multi-Level Inverter Analysis<br>symmetrical Hybrid Multi-Level Inverter (AHMLI)<br>Asymmetric Trinary Hybrid Multi-Level Inverter (THMLI)                                           | 37<br>37<br>38<br>39<br>43                                                 |

| <ul> <li>4.2 Phase</li> <li>4.3 Level-</li> <li>4.4 Hybri<br/>4.4.1 A<br/>4.4.1</li> <li>CHAPT</li> <li>5.1 Introd</li> </ul>                                                                                              | Shifted Multicarrier Modulation<br>Shifted Multicarrier Modulation<br>d Multi-Level Inverter Analysis<br>symmetrical Hybrid Multi-Level Inverter (AHMLI)<br>Asymmetric Trinary Hybrid Multi-Level Inverter (THMLI)<br>ER 5. GRID-TIED PV INVERTERS           | 37<br>37<br>38<br>39<br>43<br>43                                           |

| <ul> <li>4.2 Phase</li> <li>4.3 Level-</li> <li>4.4 Hybri<br/>4.4.1 A<br/>4.4.1</li> <li>CHAPT</li> <li>5.1 Introd</li> <li>5.2 Topol</li> </ul>                                                                           | Shifted Multicarrier Modulation<br>Shifted Multicarrier Modulation<br>d Multi-Level Inverter Analysis<br>symmetrical Hybrid Multi-Level Inverter (AHMLI)<br>Asymmetric Trinary Hybrid Multi-Level Inverter (THMLI)<br>ER 5. GRID-TIED PV INVERTERS<br>uction | 37<br>37<br>38<br>39<br>43<br>43<br>43                                     |

| <ul> <li>4.2 Phase</li> <li>4.3 Level-</li> <li>4.4 Hybri<br/>4.4.1 A<br/>4.4.1</li> <li>CHAPT</li> <li>5.1 Introd</li> <li>5.2 Topol</li> <li>5.3 Coupl</li> </ul>                                                        | Shifted Multicarrier Modulation<br>Shifted Multicarrier Modulation<br>d Multi-Level Inverter Analysis<br>symmetrical Hybrid Multi-Level Inverter (AHMLI)<br>Asymmetric Trinary Hybrid Multi-Level Inverter (THMLI)<br>ER 5. GRID-TIED PV INVERTERS<br>uction | 37<br>37<br>38<br>39<br>43<br>43<br>43<br>43                               |

| <ul> <li>4.2 Phase</li> <li>4.3 Level-</li> <li>4.4 Hybri<br/>4.4.1 A<br/>4.4.1</li> <li>CHAPT</li> <li>5.1 Introd</li> <li>5.2 Topol</li> <li>5.3 Coupl</li> <li>5.4 Grid T</li> </ul>                                    | Shifted Multicarrier Modulation                                                                                                                                                                                                                              | 37<br>38<br>38<br>39<br>43<br>43<br>43<br>43<br>44                         |

| <ul> <li>4.2 Phase</li> <li>4.3 Level-</li> <li>4.4 Hybri<br/>4.4.1 A<br/>4.4.1</li> <li>CHAPT</li> <li>5.1 Introd</li> <li>5.2 Topol</li> <li>5.3 Coupl</li> <li>5.4 Grid T</li> <li>CHAPT</li> </ul>                     | Shifted Multicarrier Modulation                                                                                                                                                                                                                              | 37<br>37<br>38<br>39<br>43<br>43<br>43<br>44<br>45<br>47                   |

| <ul> <li>4.2 Phase</li> <li>4.3 Level-</li> <li>4.4 Hybri<br/>4.4.1 A<br/>4.4.1</li> <li>CHAPT</li> <li>5.1 Introd</li> <li>5.2 Topol</li> <li>5.3 Coupl</li> <li>5.4 Grid 7</li> <li>CHAPT</li> <li>6.1 Introd</li> </ul> | Shifted Multicarrier Modulation                                                                                                                                                                                                                              | 37<br>38<br>38<br>39<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43 |

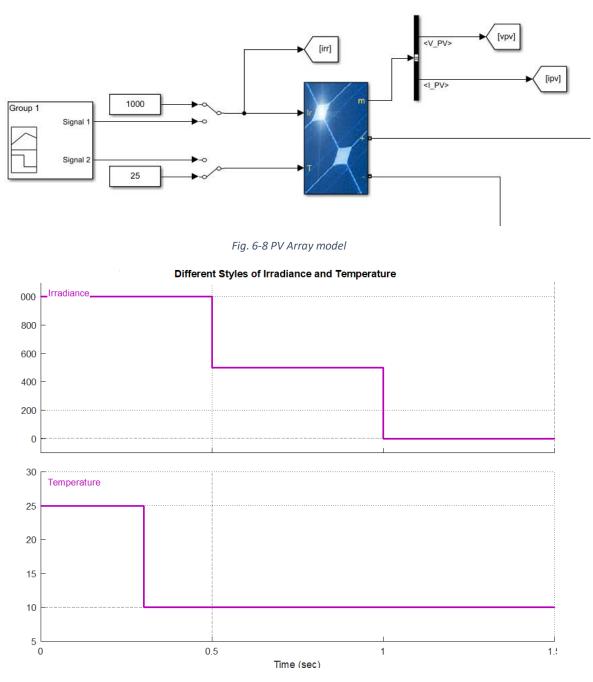

| 6.3.1 PV Array Design                                                                  | 51                                            |

|----------------------------------------------------------------------------------------|-----------------------------------------------|

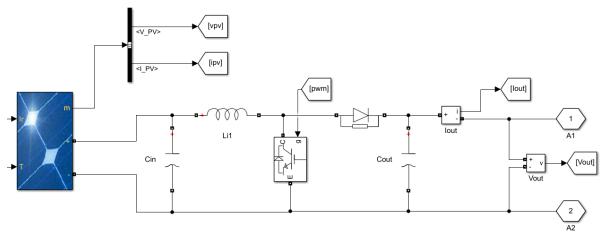

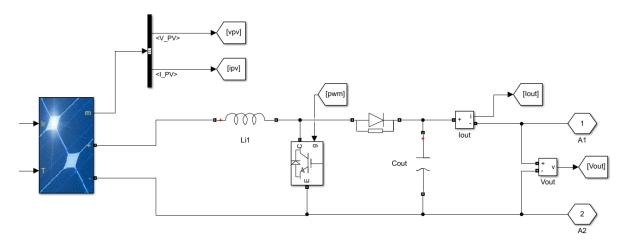

| 6.3.2 Boost Converter Design                                                           | 53                                            |

| 6.4 Coupling LCL Filter Design                                                         | 55                                            |

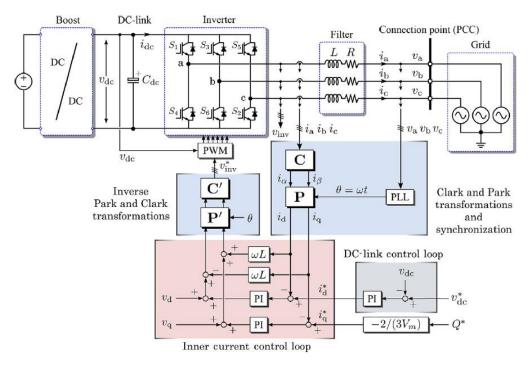

| 6.5 Active and Reactive Power Controllers                                              | 58                                            |

| 6.5.1 3-phase to the Stationary Reference Frame Transformation (Clarke Transform<br>58 | <b>mation</b> ) abc $\rightarrow \alpha\beta$ |

| 6.5.2 Stationary Reference Frame to the Synchronous Reference Frame Transform          | ation (Park                                   |

| <b>Transformation</b> ) $\alpha\beta \rightarrow dq$                                   | 58                                            |

| 6.5.3 Current Control Loop                                                             | 59                                            |

| 6.5.4 P-Q Control Loop                                                                 | 59                                            |

| 6.5.5 DC-Link Control Loop                                                             | 60                                            |

| CHAPTER 7. MATLAB/SIMULINK SIMULATION                                                  | 61                                            |

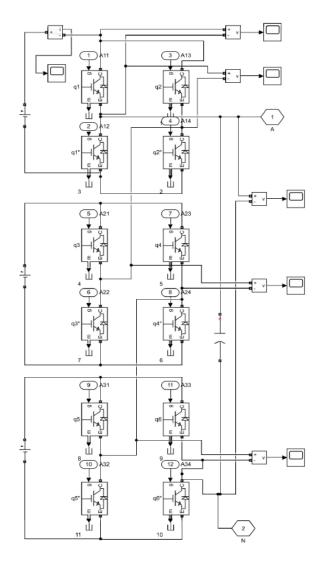

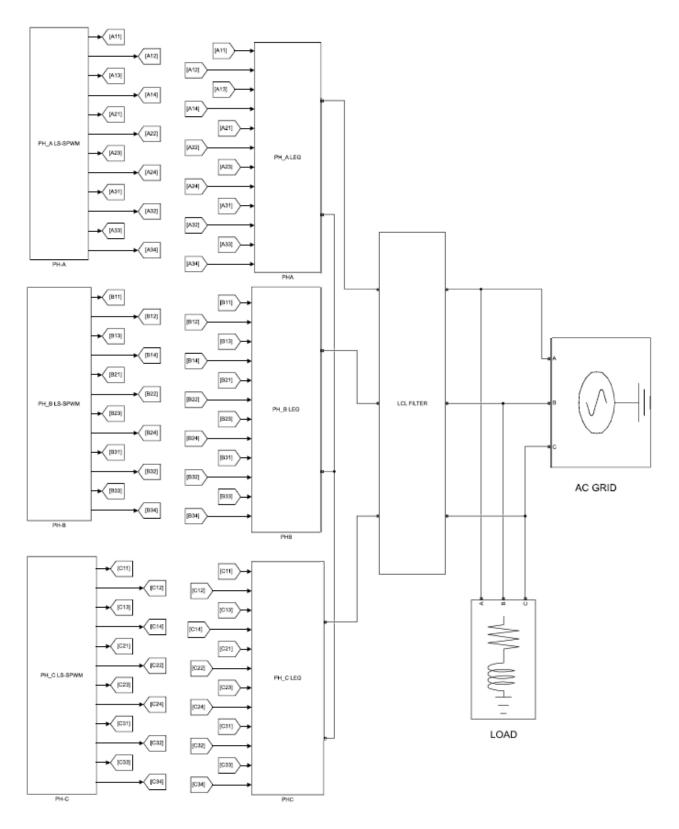

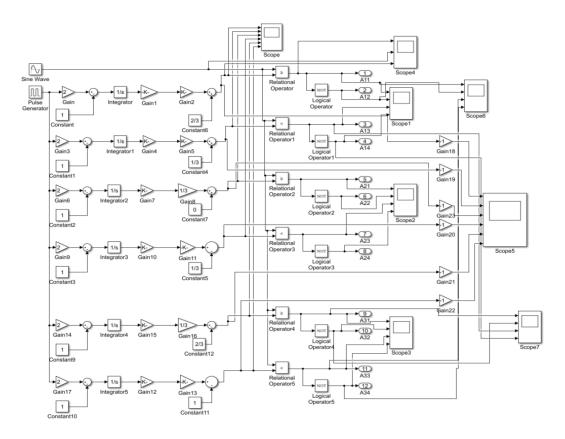

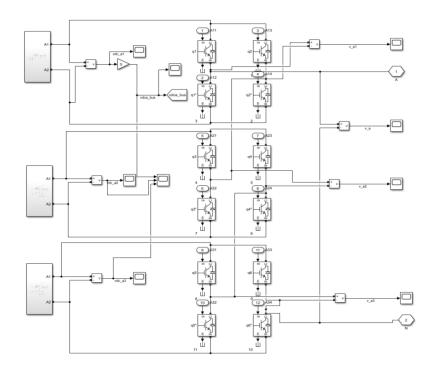

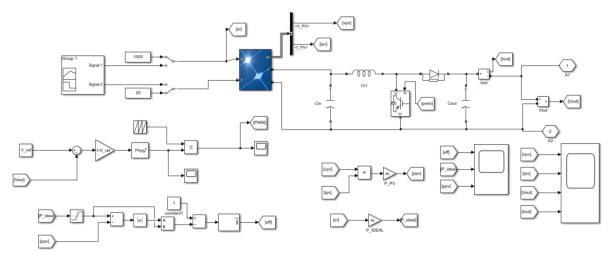

| 7.1 HMLI MATLAB/Simulink Simulation                                                    | 61                                            |

| 7.2 MATLAB/Simulink Model Parts                                                        | 61                                            |

| 7.3 Matlab Results and Analysis                                                        | 68                                            |

| 7.3.1 General Conditions – Simulation and Results                                      | 69                                            |

| 7.3.2 One Phase Conditions – Simulation and Results                                    | 76                                            |

| 7.3.3 Two Phases' Conditions – Simulation and Results                                  | 77                                            |

| 7.3.4 Output Power Injection                                                           | 78                                            |

| 7.3.5 Comparison between MLI and HMLI Inverters                                        | 79                                            |

| 7.3.6 Grid Disconnection                                                               | 80                                            |

| CHAPTER 8. CONCLUSIONS AND FUTURE WORK                                                 | 81                                            |

| 8.1 Conclusions                                                                        | 81                                            |

| 8.2 Future Work                                                                        | 81                                            |

| REFERENCES                                                                             | 82                                            |

# **Acronyms and Abbreviations**

| CSI     | Current Source Inverter                       |

|---------|-----------------------------------------------|

| FFT     | Fast Fourier Transform                        |

| HMLI    | Hybrid Multi Level Inverter                   |

| LS-SPWM | Level-Shift Sinusoidal Pulse Width Modulation |

| MLI     | Multi-Level Inverter                          |

| MPPT    | Maximum Power Point Tracker                   |

| P&O     | Perturb and Observer                          |

| PS-SPWM | Phase-Shift Sinusoidal Pulse Width Modulation |

| PV      | Photovoltaic                                  |

| PWM     | Pulse Width Modulation                        |

| RES     | Renewable Energy Sources                      |

| SPWM    | Sinusoidal Pulse Width Modulation             |

| THD     | Total Harmonic Distortion                     |

| THMLI   | Trinary Hybrid Multi Level Inverter           |

| VSI     | Voltage Source Inverter                       |

# **List of Figures**

| FIG. 2-2-1 A PV CELL EQUIVALENT CIRCUIT                                                            | 7  |

|----------------------------------------------------------------------------------------------------|----|

| FIG. 2-2-2 MAXIMUM POWER POINT OF A PV CELL                                                        | 8  |

| Fig. 2-3 Perturb and Observer algorithm [19]                                                       | 9  |

| FIG. 2-4 A BOOST CONVERTER TOPOLOGY                                                                | 10 |

| FIG. 3-3-1 THREE LEVEL THREE PHASE NPC INVERTER [23]                                               | 12 |

| FIG. 3-2 LINE TO LINE VOLTAGE WAVEFORM OF THE 3-LEVEL 3-PH NPC INVERTER [23]                       | 13 |

| FIG. 3-3 SINGLE-PHASE H-BRIDGE INVERTER                                                            | 14 |

| FIG. 3-4 FIVE-LEVEL CASCADED H-BRIDGE INVERTER                                                     | 15 |

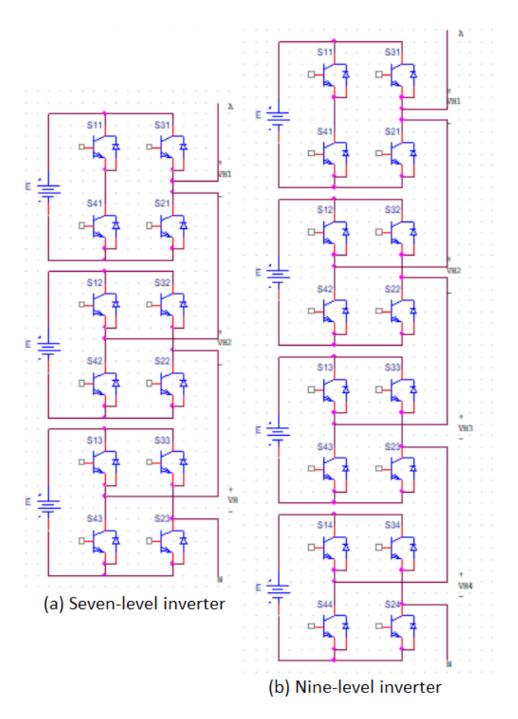

| FIG. 3-5 PER-PHASE TOPOLOGY OF (A) SEVEN- AND (B) NINE-LEVEL CHB INVERTERS                         | 16 |

| FIG. 3-6 FC MULTI-LEVEL INVERTER TOPOLOGIES FOR A) THREE LEVELS, B) FIVE LEVELS AND, C) SEVEN LEVE | LS |

| [7]                                                                                                | 17 |

| FIG. 3-7 A PWM CURRENT SOURCE INVERTER [23]                                                        | 21 |

| FIG. 3-8 REALIZATION OF THE DC CURRENT SOURCE IN PWM CSI [23]                                      | 21 |

| FIG. 3-9 PARALLEL CSIS FOR HIGH POWER APPLICATIONS [23]                                            | 22 |

| FIG. 3-10 LCI FOR SM DRIVE [23]                                                                    | 23 |

| FIG. 3-11 NEGATIVE POLARITY BOOST-TYPE CSI                                                         | 24 |

| FIG. 3-12 POSITIVE POLARITY BOOST-TYPE CSI                                                         | 25 |

| FIG. 3-13 LC CURRENT SOURCE INVERTER                                                               | 25 |

| FIG. 3-14 THREE-LEVEL DUAL PWM CURRENT SOURCE INVERTER                                             | 27 |

| FIG. 3-15 FIVE-LEVEL EMBEDDED MULTI-LEVEL CSI                                                      |    |

| FIG. 3-16 TWO-STAGE MULTI-LEVEL CSI [34]                                                           |    |

| FIG. 3-17 Semi-two-stages Multi-Level [34]                                                         |    |

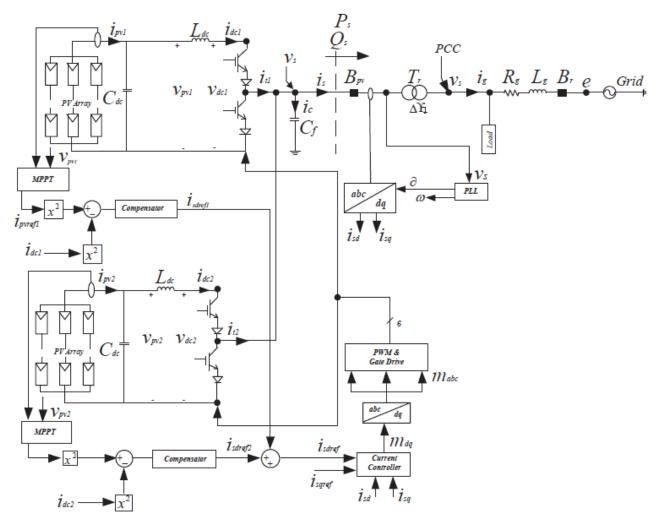

| FIG. 3-18 PARALLEL MULTI-LEVEL CSI WITH CONTROLLERS IN PV APPLICATIONS [43]                        | 29 |

| FIG. 3-19 SINGLE RATING INDUCTOR MULTI-LEVEL CSI [52]                                              | 30 |

| FIG. 3-20 FIVE-LEVELS BACK TO BACK MULTI-LEVEL CSI [46]                                            | 31 |

| FIG. 3-21 REDUCED COUNT SWITCHES MULTI-LEVEL CSI [48]                                              | 32 |

| FIG. 3-22 FIVE-LEVELS PARALLEL INDUCTOR MULTI-LEVEL CSI [49]                                       |    |

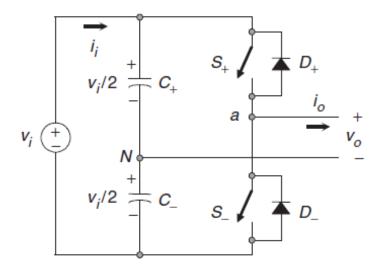

| FIG. 4-1 SINGLE PHASE HALF-BRIDGE VSI [1]                                                          | 35 |

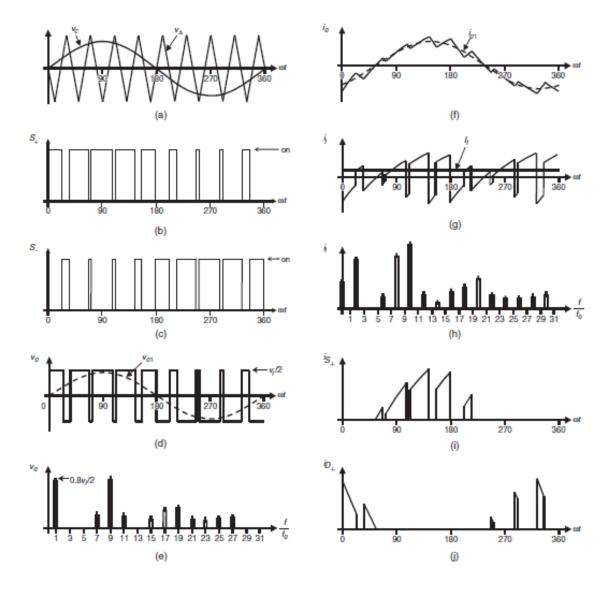

| FIG. 4-2 The half-bridge VSI. Ideal waveforms for the SPWM ( $Ma = 0.8, Mf = 9$ ): (a) carrier and |    |

| MODULATING SIGNALS; (B) SWITCH S+ STATE; (C) SWITCH S– STATE; (D) AC OUTPUT VOLTAGE; (E) AC        |    |

| OUTPUT VOLTAGE SPECTRUM; (F) AC OUTPUT CURRENT; (G) DC CURRENT; (H) DC CURRENT SPECTRUM;           |    |

| SWITCH S+ CURRENT; AND (J) DIODE D+ CURRENT [1]                                                    |    |

| FIG. 4-3 SINGLE PHASE FULL-BRIDGE INVERTER [1]                                                     |    |

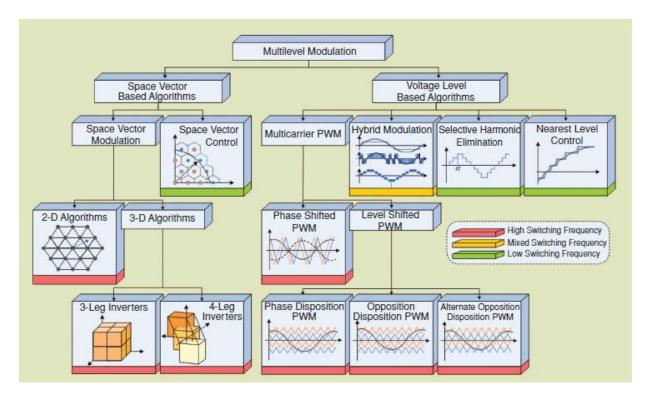

| FIG. 4-4 CLASSIFICATION OF MODULATION TECHNIQUES FOR MULTI-LEVEL INVERTERS [56]                    |    |

| FIG. 6-1 PHASE A STRUCTURE                                                                         |    |

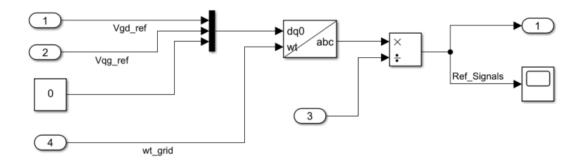

| FIG. 6-2 GENERATION PROCESS OF THE REFERENCE SIGNALS                                               |    |

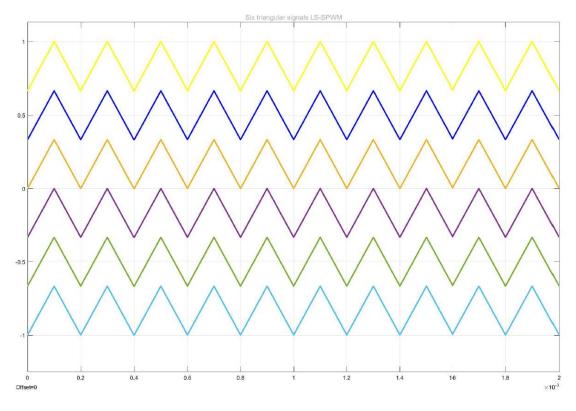

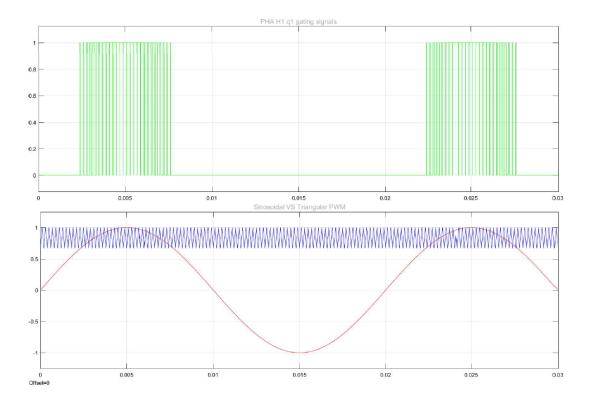

| FIG. 6-3 SIX TRIANGULAR LS-SPWM SIGNALS                                                            |    |

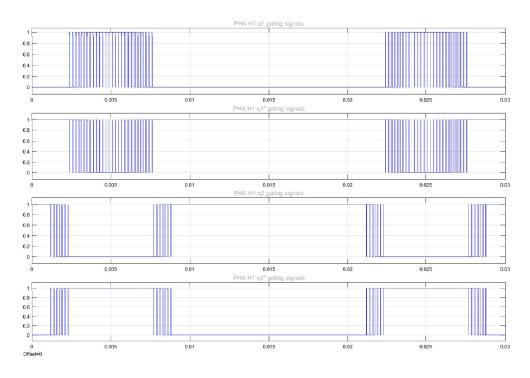

| FIG. 6-4 PHA HB1 GATE SIGNALS.                                                                     | -  |

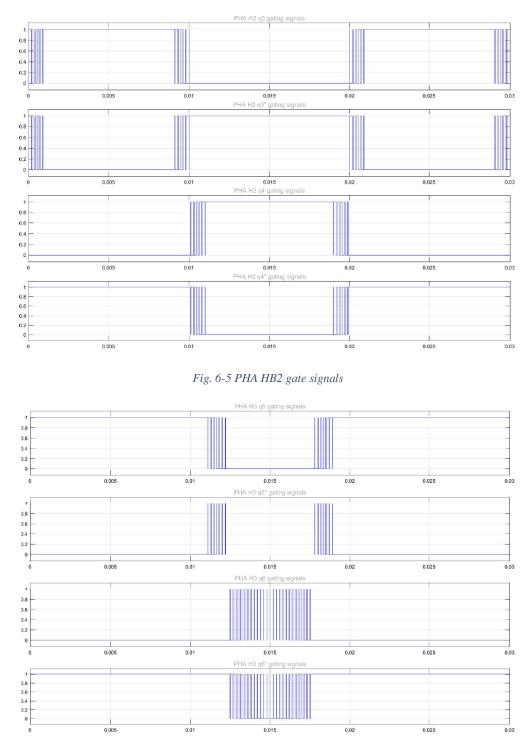

| FIG. 6-5 PHA HB2 GATE SIGNALS.                                                                     |    |

| FIG. 6-6 PHA HB3 GATE SIGNALS.                                                                     |    |

| FIG. 6-7 HB1 PHA Q1 SINUSOIDAL VS TRIANGULAR PWM                                                   |    |

| FIG. 6-8 PV ARRAY MODEL                                                                            |    |

| FIG. 6-9 ENVIRONMENTAL CONDITIONS - VARIOUS IRRADIATION AND TEMPERATURE                            |    |

| FIG. 6-6-10 BOOST CONVERTER                                                                        |    |

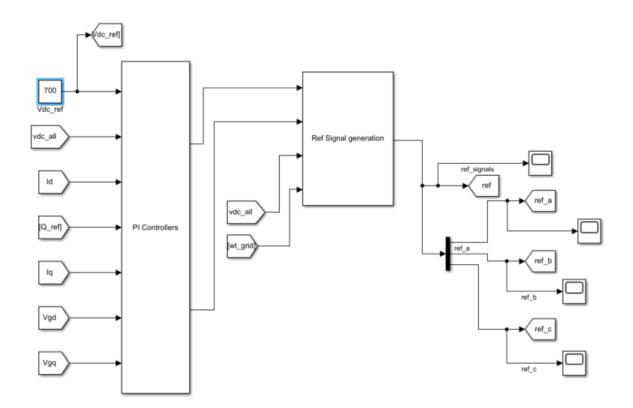

| FIG. 7-1 GENERAL OVERVIEW OF THE HMLI                                                              |    |

| FIG. 7-2 THMLI LEVEL-SHIFT PULSE WIDTH MODULATION GENERATION BLOCKS                                |    |

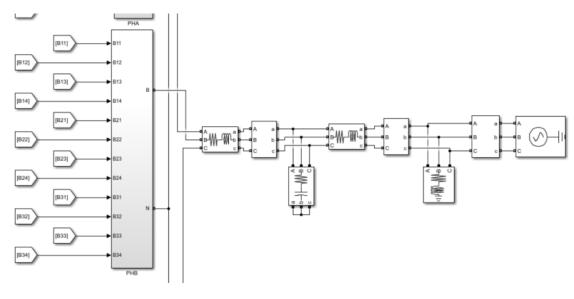

| FIG. 7-3 PhaseA Schematic Structure                                                                |    |

| FIG. 7-4 PV ARRAY DESIGN.                                                                          |    |

| Fig. 7-5 Boost Converter Model                                                                     | 64 |

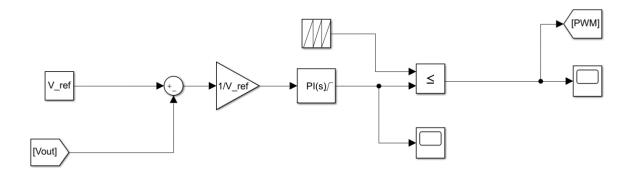

| FIG. 7-6 BOOST CONVERTER CONTROLLER                                                        | 65 |

|--------------------------------------------------------------------------------------------|----|

| FIG. 7-7 LCL FILTER CONNECTION                                                             | 65 |

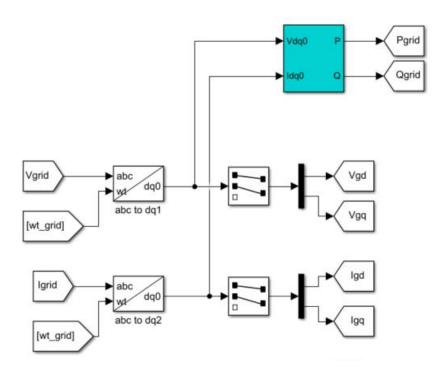

| Fig. 7-8 Grid ABC to DQ CONVERSION                                                         | 66 |

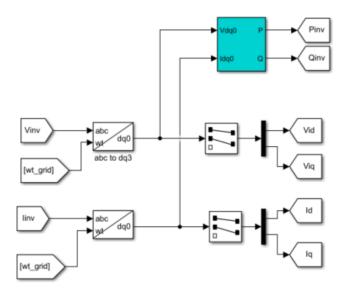

| Fig. 7-9 Inverter ABC to DQ CONVERSION                                                     | 66 |

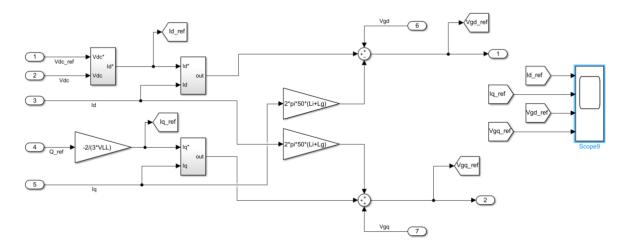

| Fig. 7-7-10 Vdc, P, and Q Controllers                                                      |    |

| FIG. 7-11 ID_REF, IQ_REF, VD_REF AND VQ_REF CONTROLLERS                                    | 67 |

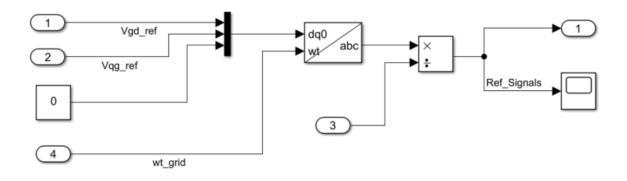

| FIG. 7-12 REFERENCE SIGNALS GENERATION                                                     | 68 |

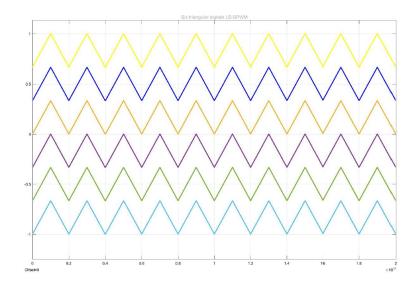

| Fig. 7-13 Six triangular LS-SPWM signals                                                   | 68 |

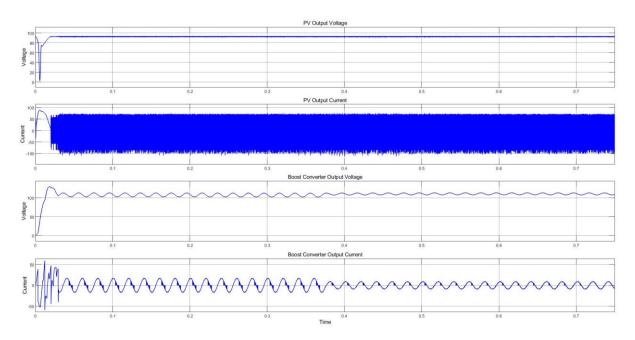

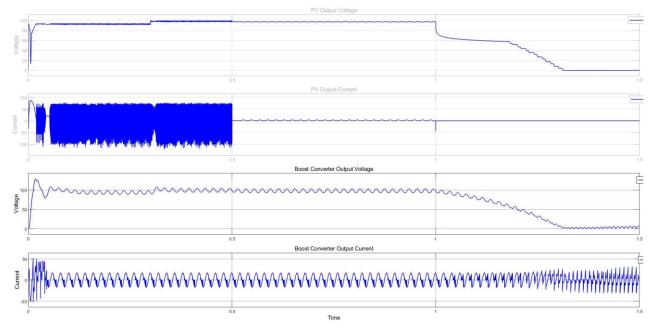

| FIG. 7-14 INPUT AND OUTPUT VOLTAGES AND CURRENTS OF THE PV ARRAY - 2ND LEG OF THE INVERTER | 69 |

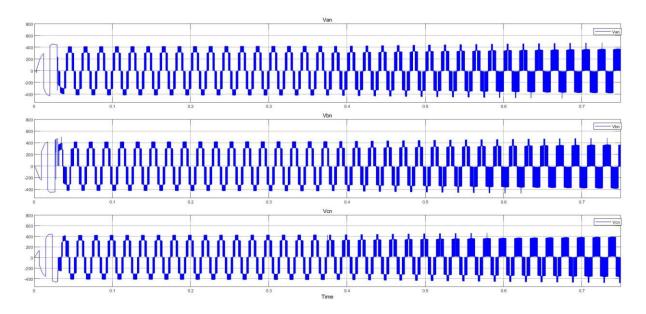

| FIG. 7-15 L-N VOLTAGE LEVELS                                                               | 70 |

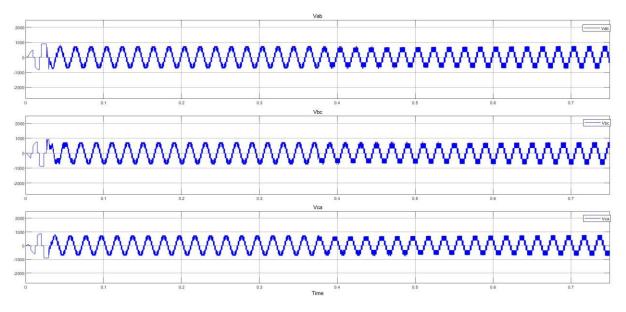

| FIG. 7-16 L-L VOLTAGE LEVELS                                                               |    |

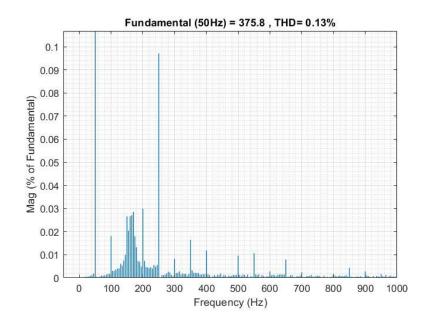

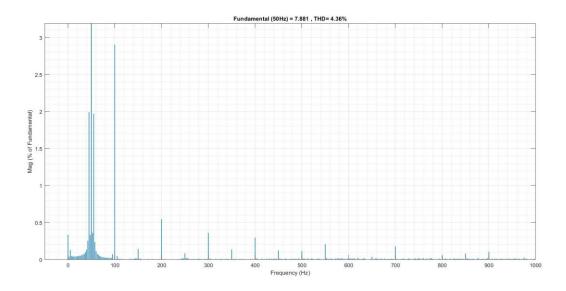

| Fig. 7-17 Fast Fourier Transform for V_(L-L)                                               | 71 |

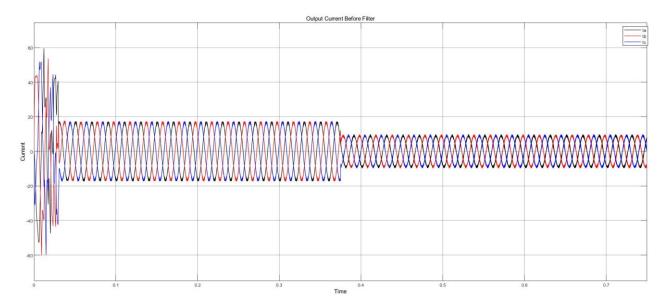

| Fig. 7-18 Inverter Current before the Filter                                               | 71 |

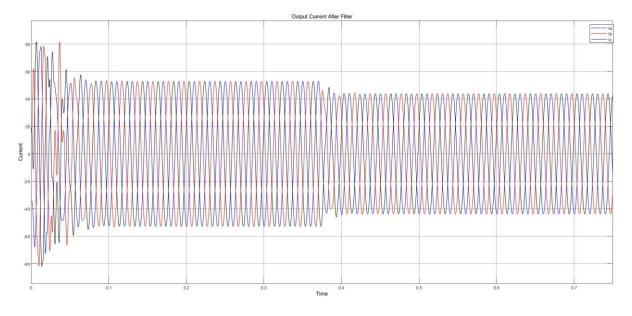

| Fig. 7-19 Inverter Current after the Filter                                                | 72 |

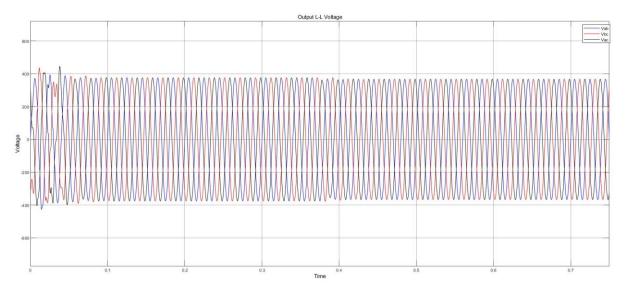

| Fig. 7-20 Output Voltage of the Inverter                                                   | 72 |

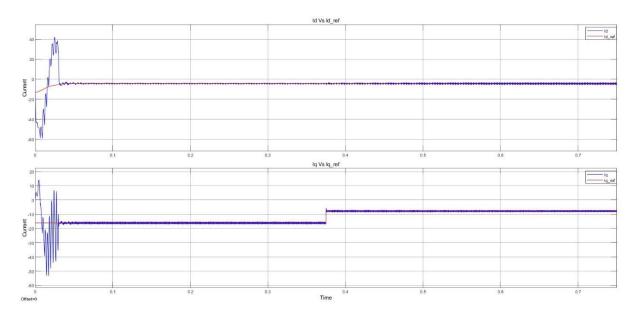

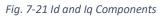

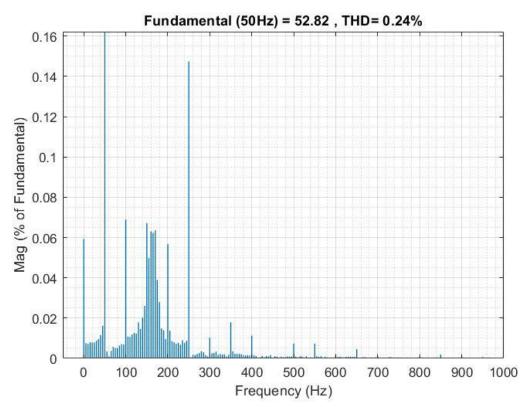

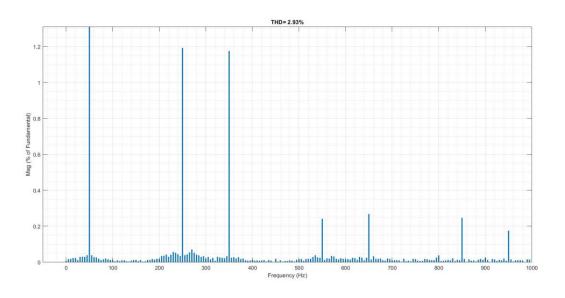

| FIG. 7-21 ID AND IQ COMPONENTS                                                             | 73 |

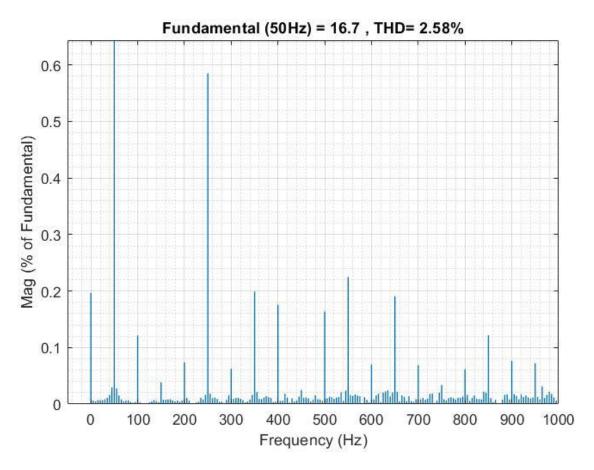

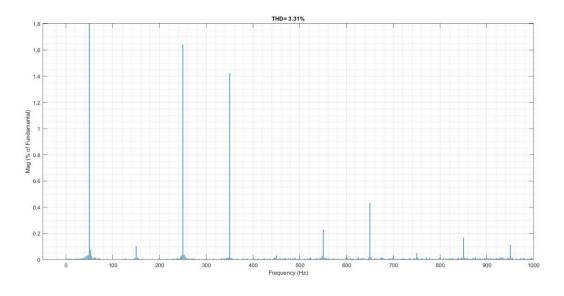

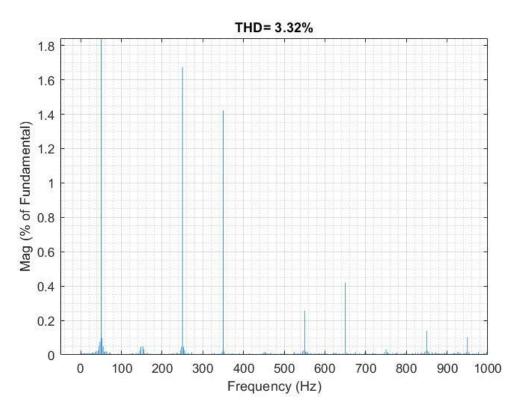

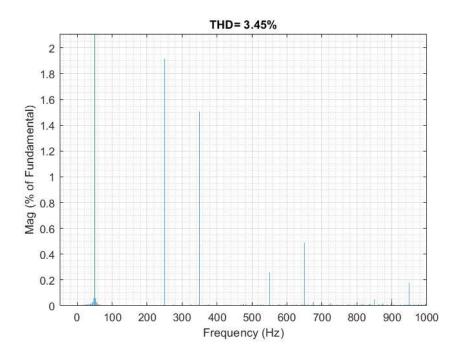

| FIG. 7-22 THD OF THE OUTPUT CURRENT BEFORE THE FILTER                                      |    |

| FIG. 7-23 THD OF THE OUTPUT CURRENT AFTER THE FILTER                                       | 74 |

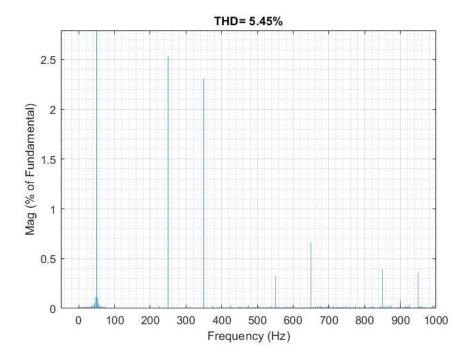

| FIG. 7-24 THD OF THE OUTPUT CURRENT BEFORE THE FILTER AT 15 DEGREES CELSIUS                | 75 |

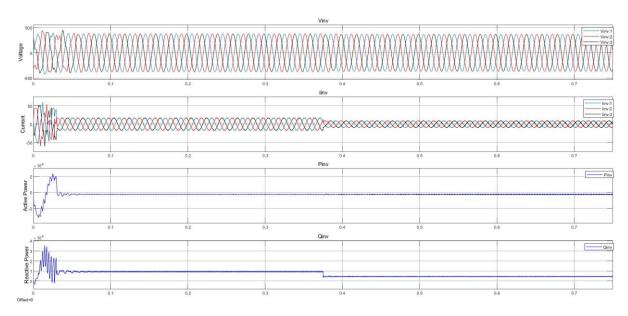

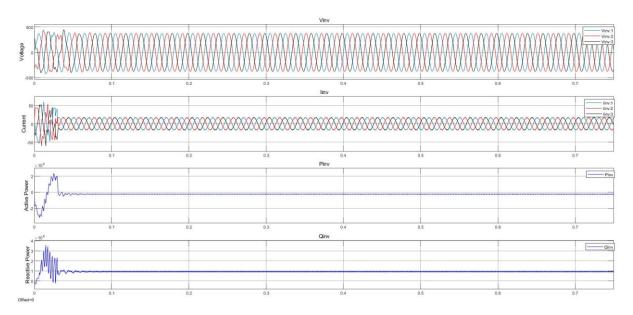

| FIG. 7-25 OUTPUT VOLTAGE, CURRENT, ACTIVE POWER AND REACTIVE POWER                         | 75 |

| FIG. 7-26 PV OUTPUT VOLTAGE AND CURRENT IN THE PARTIAL SHADING CONDITION                   | 76 |

| FIG. 7-27 THD VALUE IN THE PARTIAL SHADING CONDITIONS - ONE PHASE                          | 77 |

| FIG. 7-28 THD VALUE IN THE PARTIAL SHADING CONDITIONS - TWO PHASES                         | 77 |

| FIG. 7-29 THD OF THE OUTPUT CURRENT AT THE FULL POWER CAPACITY INJECTION                   | 78 |

| FIG. 7-30 THD OF THE OUTPUT CURRENT AT THE HALF POWER CAPACITY INJECTION                   | 78 |

| FIG. 7-31 POWER REFERENCE EFFECT ON THE OUTPUT VOLTAGE, CURRENT AND POWER                  | 79 |

| FIG. 7-32 THD OF THE MLI UNDER THE SAME CONDITION OF THE HMLI                              | 80 |

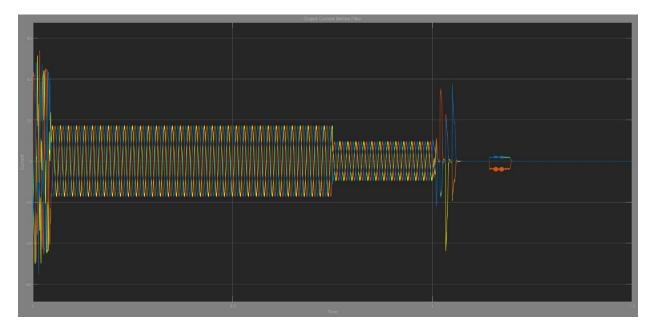

| Fig. 7-33 Grid Disconnection Case in the THMLI                                             | 80 |

## **List of Tables**

| TABLE 4-1 RELATIONSHIP BETWEEN THE INPUT AND OUTPUT VOLTAGES OF A SINGLE HB MODULE IN THE THMLI | 40 |

|-------------------------------------------------------------------------------------------------|----|

| TABLE 6-1 PV ARRAY DESIGN PARAMETERS                                                            | 52 |

# **Chapter 1. Introduction**

Despite the attractive features of renewable energy resources such as availability, sustainability, and being environment friendly, more challenges regarding their utilization and implementation in power systems have to be tackled.

### **1.1 Introduction**

It has been very attractive for researchers to propose new technologies that facilitate human's life and solve their technical problems. Among their trend to increase the use of clean energy resources, the focus on developing power electronics devices is increasing enormously. This thesis focuses on studying one of the most important parts of the Photovoltaic (PV) system, which is the DC-to-AC converter; especially studying the latest updated topologies in the last two decades; "the Hybrid Multi-Level Inverters (HMLI)". Most HMLI used in the PV application will be selected, studied, simulated and analyzed. Specific indices will be chosen within this thesis, to determine the most appropriate and efficient topology that would be the best in PV applications.

### **1.2 Problem Statements**

The Hybrid Multi-Level Inverter with both types of sources (voltage and current) are surveyed, studied and analyzed. This work implements hybrid inverters in photovoltaic systems applications. A comparison between voltage and Current Source Inverters is held to get the most efficient inverter that would be used in photovoltaic systems.

### **1.3** Contribution

This thesis proposes the implementation of the Trinary Hybrid Multi-Level Inverter in the PV systems. The contributions of the thesis can be described as follows:

- Introduction of a modular inverter with 3 different levels of voltages. That provides flexible design and easy maintenance procedures.

- Providing a design topology capable to accommodate the various conditions of environmental conditions.

- Providing a comprehensive and adaptive control method for the injected power into the grid and the DC-link voltage.

### **1.4 Research Goals**

This research aims to:

- Present the latest Hybrid Multi-Level Inverters (HMLIs) recently proposed by researchers

- Hold a comparison between HMLIs based on many indexes mentioned later in this thesis

- Modeling the HMLI in a photovoltaic system, modeling, simulating and analyzing the results using MATLAB/Simulink

### **1.5 Organization of the Thesis**

This thesis report is divided into eight chapters that have the following brief descriptions:

- Chapter 2 introduces the relationship between renewable energy sources and power electronic devices and demonstrates a brief historical introduction of power electronic converters and presents most problems that new technologies had solved in the last few decades. Also, it presents an introduction to the PV structure and popular algorithms and power electronic devices that are usually used within PV system implementation.

- Chapter 4 describes how and why researchers are in favor of replacing Multi-Level Inverters by the Hybrid Multi-Level Inverters. It demonstrates the most well-known voltage and current source Multi-Level Inverters. Besides, it presents most of the modulation techniques used to control Multi-Level Inverters. On the other side, it demonstrates the Hybrid Multi-Level Inverters surveyed through the literature review, lists their advantages and drawbacks, and compares between them using comparing indexes list within the thesis.

- Chapter 5 introduces the grid-tied inverters. It discusses the new technologies and topologies of them. It also focuses on the coupling filters between the inverters and the grid.

- Chapter 6 presents the design procedure for the whole parts of the inverter; starting from the PV system, boost converter, modulation techniques, coupling filter and controllers.

- Chapter 7 demonstrates the MATLAB model simulation and results. It discusses the results based on the theory described in the literature review.

- Chapter 8 draws out conclusions and sets out future work plan.

# **Chapter 2.** Literature Review

#### **2.1 Introduction**

The fast development of the Renewable Energy Systems (RESs) in the last few decades, made it very necessary to improve required power devices to make use of, especially the power converters and inverters. Continuous researches and studies were focused on various types of power electronic devices that convert power from AC to DC and vice versa. Starting from the most traditional one, the two-level converters, to the Multi-Level ones in the last two decades, and ending by the newest ones, the hybrid Multi-Level ones.

Although, they are very simple, traditional power inverters, which are also referred as twolevel power inverters have many drawbacks. Their output harmonic components are very large, and so the Total Harmonic Distortion (THD) is very high. Since they are two-level inverter, the voltage variation with respect to time  $\frac{dv}{dt}$  is very large, that makes sever stress on power switches of the inverter. Also, they operate on very high values of the switching frequency, which increases switching losses within the power electronic devices. On the other side, their application are limited to the low and medium voltage ranges [1], [2].

Multi-Level Inverters (MLIs) were first introduced in 1975 by Baker and Banisster [3]. They introduced the cascaded H-Bridge inverter. Then the Neutral Point Clamped inverter (NPC) was introduced by Baker in 1980 [4]. After that, the Flying Capacitor (FC) inverter was introduced by Meynard and Foch in 1992 as a modification to the NPC one, they used clamping capacitors instead of the diodes [5].

#### 2.2 Features of Multi-Level Inverters

Multi-Level Inverters (MLIs) have many attractive features that raised their use in the last decades, which can be summarized as follows [1], [2], [6]–[8]:

#### 1- Staircase waveform quality

Which means less  $\frac{dv}{dt}$  rate, less stress across inverter switches and the Electromagnetic Compatibility (EMC) will be reduced accordingly. In addition, the harmonic components will be reduced in the output waveforms.

#### 2- Common-Mode Voltage (CM)

A MLI produces smaller CM voltage. In motor drive application, the stress on the motor bearings will be reduced [1].

#### 3- Low distortion in the Input Current

MLIs can draw input current with a low distortion [1].

#### 4- Wide Range of Switching Frequency

On the contrary to the two-level inverters, the MLI can operate at both fundamental switching frequency and high switching frequency Pulse Width Modulation (PWM) schemes. That means less switching losses. And so, a more efficient inverter.

#### 5- Reduced Number of Components

In some cases, newly proposed MLIs in recent researches have less components of power switches, diodes, or capacitors.

#### 6- Modular Topology (Redundancy)

Some types of MLIs have the property of modularity. That means the ease of maintenance and more availability of output power.

Nevertheless, MLIs have some drawback that can be summarized as follows [2], [9]:

#### 1- High Number of Power Switches

In most cases, the high number of the switches is the most important problem in the MLI.

#### 2- Control Complexity

MLI must be precisely controlled to get the best required output waveform.

#### 3- Voltage balancing of the inverter capacitors

Some types of MLIs face the problem of the unbalance voltages cross their capacitors. That is due certain operating conditions, the value of the modulation index, the dynamic behavior and load conditions [10].

#### 2.3 What is Hybrid?

Due to the previous mentioned drawbacks of the conventional Multi-Level Inverters, researcher have been doing their best to introduce more kinds of inverters tackling those obstacles. Hybrid Multi-Level Inverters (HMLI) were introduced. Basically, HMLIs are derived as a combination of the conventional MLIs. That is what the word "Hybrid" points to. Actually, Hybrid corresponds to one of the followings [11]:

#### 1- Hybrid source:

In this topology of inverters, the input power sources ,voltage or current, are different or unequal for each cell [7], [12], [13].

#### 2- Hybrid configuration:

This topology of inverters has two or more type of conventional two-level inverters or Multi-Level ones [14].

#### 3- Hybrid device:

In this topology, additional devices and power elements are added to the conventional topology of the MLI. This may include power diodes, capacitors, switches or transformers [15]–[17].

All possible Hybrid Multi-Level Inverters (HMLIs) are considered to solve one or more of the problems that the conventional Multi-Level Inverters face. They might reduce the harmonic components in the output waveform, and thus the value of Total Harmonic Distortion (THD). Also, they reduce the power switching and conduction losses in the reduced topologies of HMLI. HMLIs may be used to regulate the voltage among the DC link capacitors of the inverter, or to get more flexible number of output waveform levels.

Despite the huge number of the Multi-Level and Hybrid Multi-Level studies, focused on the voltage-source MLIs, very few studies focus on the current-source MLIs; the Multi-Level Current Source Inverter has drawn little concern. One can easily figure that, there are great

efforts and trials to classify voltage-source MLIs, but it's the opposite for the current-source MLIs; whose classifications still need more and more attention and reviews [1], [7], [18].

#### 2.4 Photovoltaic Systems

#### **2.4.1 Introduction**

The large technological and industrial revolution in the last couple of centuries depended mainly on the bulk demand of the fossil fuel. In the last few years, scientists declared that it would be difficult to depend completely on that type of fuel. That is because, it is a nonrenewable source of energy, which has a relatively high cost, and has bad effects on environment and causes pollution.

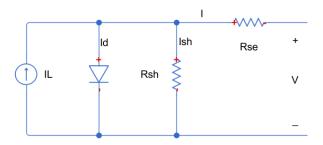

Renewable energy resources began to take its role significantly in the last few decades. Photovoltaic (PV) solar system was one of the most importantly introduced resources. PV systems are clean, emission-free, and plentiful. Simply, the PV system converts the photon energy into electrical one. It basically consists of PV arrays, a DC-to-DC converter implementing a maximum power point tracker algorithm, and a DC-to-AC converter (inverter). The PV array consists of a multiple number of PV modules, each module consists of multiple solar cells, that can be electrically modelled as in Fig. 2-1 [19].

Fig. 2-2-1 A PV cell equivalent circuit

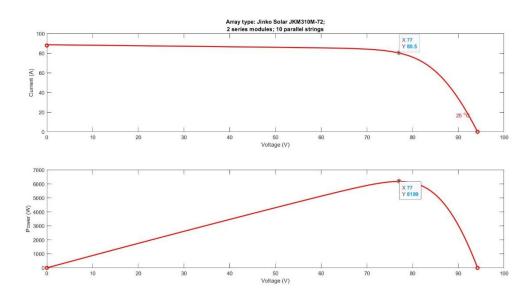

Actually, the output voltage and current of the solar cell depends on many factors. Thus, they always change as these factors change. Manufacturing materials, ambient temperature and the rate of radiation are the most effective factors that specify the output of the PV module. In addition, the current delivered to load also affects the PV module efficiency [13], [20]. It is desired to keep the power delivered out of the PV module as maximum as possible. Many algorithms were proposed to operate the PV module at a point that gives the maximum output power whatever the affecting factors were. These algorithms are called the Maximum Power Point Trackers (MPPT). One of the most common MPPT methods is the Perturb and Observe (P&O) [19]. Fig. 2-2 shows how to determine the Maximum Power Point (MPP) of a PV cell depending on the output power yield.

Fig. 2-2-2 Maximum power point of a PV cell

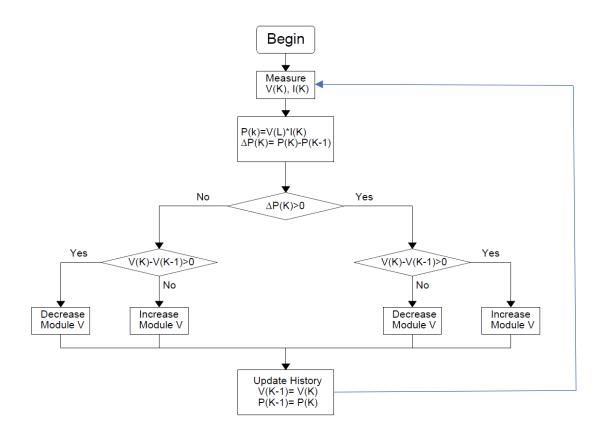

#### 2.4.2 Perturb and Observer MPPT

One of the most popular MPPT algorithms is the Perturb and Observer (P&O) [19]. That is because it's simple and easy to implement. It basically depends on two mechanisms: 1) Perturb the input and 2) observe the output. The tracker tries to find the Maximum Power Point (MPP) by incrementing or decrementing the PV operating voltage and observing the resulting output power. The way of changing the PV voltage (incrementing or decrementing) in which the output power approaches to the value of the MPP must be kept and followed. But, if the output power value drifts away from the value of the MPP, the change in the voltage must be reversed. Fig. 2-3 depicts a flowchart explaining the method of the P&O algorithm.

Fig. 2-3 Perturb and Observer algorithm [19]

In addition to achieving the maximum output power of the PV system, it is also required to get a stable DC output of the system that can act as a perfect input for the DC to AC converters. That could be achieved using a DC-to-DC converter. Depending on the desired output of the converter, the type (Boost, SEPIC or Cuk) and the input of the DC-to-DC converter can be easily determined.

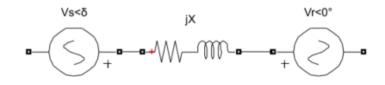

#### 2.4.3 Step-up (Boost) Converter

DC-to-DC converters are usually used in DC power supplies, Uninterruptable Power Supplies (UPSs), DC motor drives and renewable energy applications. The input of the DC-to-DC converter is usually unregulated DC voltage, which can be an output from a rectifier or an output for a Photovoltaic (PV) array system. It is common in these cases, to have an unstable output voltage that may have considerable variations and fluctuations.

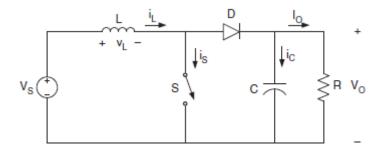

It is used to use the Step-up (Boost) converters in the PhotoVoltaic (PV), to raise the output voltage of the PV array to a considerable value suitable for most applications [21]. As shown in Fig. 2-4, the Boost converter basically consists of a DC input voltage source  $V_s$ , Boost inductor L, controlled switch S, diode D, and a filter capacitor C.

Fig. 2-4 A Boost converter topology

When the switch S is on, the current in the inductor increases linearly. And when it is off the current decrease linearly and the stored energy is dissipated in the RC circuit. Eq. (2.1) shows the relation between the input voltage  $V_s$  and the output voltage  $V_o$ .

$$V_s DT = (V_o - V_s)(1 - D)T$$

(2.1)

where D is the duty ratio and is defined as the ratio between the switch on time to the sum of the on and off times. Accordingly, the relation between the output voltage and input voltage is described by eq. (2.2);

$$\frac{V_o}{V_s} = \frac{1}{1 - D}$$

(2.2)

# Chapter 3. Multi-Level and Hybrid Multi-Level Inverters

Mainly, Multi-Level and Hybrid Multi-Level Inverters are classified into two types; voltagesource inverters and current source inverters. It is common that, only different types of sources and loads can be connected to each other; the voltage source can be directly connected to a current type load and current sources can be directly connected to a voltage type load. The purpose of such criterion is to avoid the parallel connection between two voltage-type elements, and so preventing short-circuit between them or avoid connecting two current sources in series [22], [23].

### **3.1Voltage Source Inverters (VSIs)**

The output waveform of this type of inverters is an independently controlled voltage waveform. It's a fully controlled magnitude, frequency and phase shift output. VSIs are very commonly used inverters as they naturally behave as voltage sources, that are required by most of industrial, medium and high voltage applications [1], [24].

VSIs are categorized into three main categories; the two-level inverters, Multi-Level Inverters and the Hybrid Multi-Level Inverters. Two-level inverters will not be taken into consideration here, the Multi-Level Inverters will be briefly described to get the concept of the Multi-Level techniques, and the Hybrid Multi-Level Inverters will be deeply described, analyzed and simulated.

#### 3.1.1 Multi-Level Voltage Source Inverters

The shape of the output waveform for this type of inverters looks like a staircase. The number of levels varies from 3 up to 81 levels, or more. It depends on the inverter topology, number of switches and the modulation technique used. There are three basic types of Multi-Level Inverters commonly named traditional or conventional Multi-Level Inverters. Those are Neutral Point Clamped inverter, cascaded H-bridge inverter and Flying Capacitor inverter. Each of these inverter types can be configured or constructed depending on the number of used

switches and supporting diodes or capacitors to produce a different level type of the same schematic.

#### 3.1.1.1 Neutral Point Clamped (NPC) Inverter

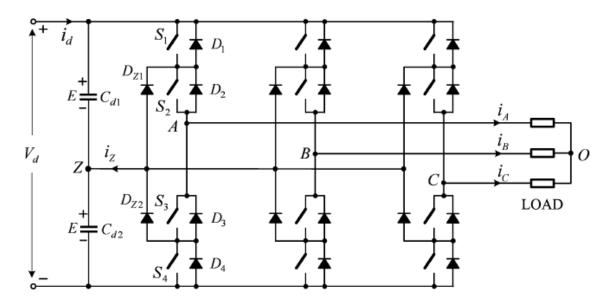

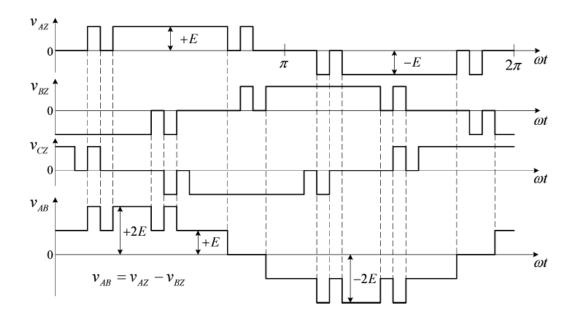

It is also known as Diode Clamped inverter. It is one of the most common topologies for medium and high-level voltage applications, especially for motor drive applications. It has many advantages such as; reduced dv/dt rate, reduced Total Harmonic Distortion (THD) and its ability to deal with high voltage demand without connecting switches in series [1], [22], [23]. However, it can be also used in low voltage applications such as the photovoltaic systems, where other factors like the voltage with low distortion and reduced leakage current are very important. Fig. 3-1 shows the three-phase three-level configuration of the NPC inverter. Whilst, Fig. 3-2 shows the output waveforms of the inverter, which shows the expected staircase shape of the output.

Fig. 3-3-1 Three level three phase NPC inverter [23]

NPC inverter has one major problem, which is related to the DC-link capacitor voltage and its control process. The neutral point voltage,  $v_z$ , varies with the operating conditions of the NPC inverter [22]. The DC-link capacitors are charged and discharged by the neutral current  $i_z$ , causing neutral-point voltage deviation. Besides, other factors may affect the neutral point voltages, such as [23]:

Fig. 3-2 Line to line voltage waveform of the 3-level 3-ph NPC inverter [23]

- Unbalanced DC capacitors due to manufacturing tolerances

- Inconsistency in switching device characteristics

- Unbalanced three-phase operations

Many control processes were introduced to solve the neutral point voltage deviation in the NPC inverter, where the voltage deviation is detected and then controlled again [25], [26]. In addition, although each active switching device is only required to block a voltage level of  $V_{dc/(m-1)}$ , the clamping diodes must have different voltage ratings for reverse voltage blocking [6]. Besides, as the number of required levels is increased, the control process of the NCP inverter becomes more complex.

#### 3.1.1.2 Cascaded H-Bridge Inverter

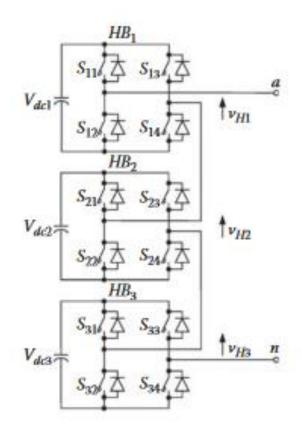

Cascaded H-bridge inverter is one of the most popular inverters used in medium voltage applications. It is constructed from multiple units of single-phase H-bridge power cell as shown in Fig. 3-3.

Fig. 3-3 Single-phase H-bridge inverter

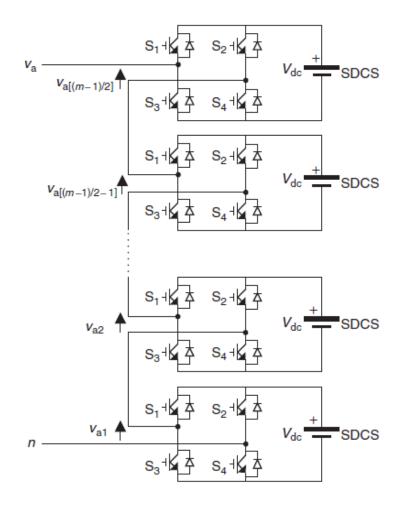

Those single-phase H-bridge power cells are connected in cascade to get the desired medium voltage level and the low value of the total harmonic distortion. Practically, the number of cells is determined according to the operating voltage and the manufacturing cost. Actually, using equal DC H-bridge cells in the inverter leads to the property of modularity and therefore, a reduction of the manufacturing cost [23]. However, more levels can be obtained when unequal DC power supplies are used.

For equal DC sources, the level's number of the output waveform depends directly on the number of the used H-bridge cells of the inverter. It can be given by eq. (3.1).

$$m = 2H + 1 \tag{3.1}$$

Where, m is the number of the output levels, and H is the number of the single-phase H-bridge power cells. This equation is only valid for cascaded H-bridge inverters with equal DC voltage input of the cells (traditional H-bridge inverter). Inverters having different values for their input

cells have a different consideration according to the criterion followed in choosing the input DC voltages, and they will be discussed later in Chapter 4.

Cascaded H-bridge inverters have many advantages that other Multi-Level Inverters don't have, such as: (i) simple packaging and physical structure (ii) ability to operate during fault occurrence in one or more of H-bridge power cells (iii) modular structure which leads to fast and simple maintenance operations. However, they give some disadvantages such as: (i) high number of isolated DC sources (ii) complex control for increased number of output waveform levels. In PV system application, it is too easy to maintain the required DC voltage inputs for the cascaded H-bridge Multi-Level Inverter. That is the reason for the widespread use of them in such applications, and it will be also discussed later on in upcoming sections. Fig. 3-4 and Fig. 3-5 show different topologies of the cascaded H-bridge inverter that give 5, 7 and 9 levels, respectively.

Fig. 3-4 Five-level cascaded H-bridge inverter

Fig. 3-5 Per-phase topology of (a) seven- and (b) nine-level CHB inverters

The total number of used switches in the cascaded H-bridge inverter is given by eq. (3.2)

$$N_{sw} = 2 * (m - 1) \tag{3.2}$$

Where, m is also the number of desired levels in the output waveform.

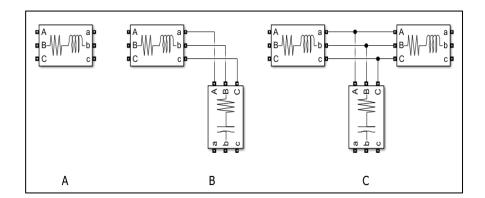

#### 3.1.1.3 Flying Capacitor Multi-Level Inverter

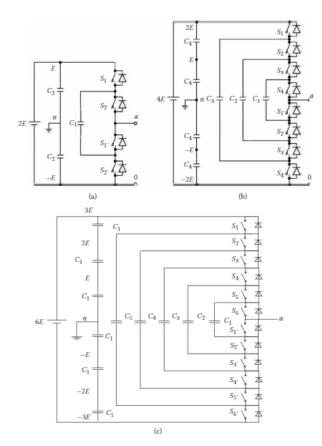

The structure of this inverter is similar to that of the diode-clamped inverter except that, instead of using clamping diodes, the inverter uses capacitors. On the contrary to the NPC inverters, Flying Capacitor inverters (FC) present higher degree of freedom (redundant states) to synthesize a specific output voltage and employ a lesser number of power electronic devices. This property of higher states of redundancy enables the inverter to regulate its capacitors' voltage correctly and easily [1], [2], [7], and [18]. In addition, the use of high frequency switching is recommended in the FC inverters to quickly balance the charge between the flying capacitors of the inverter. Fig. 3-6 shows different topologies of the FC inverters for different number of levels.

*Fig. 3-6 FC Multi-Level Inverter topologies for a) three levels, b) five levels and, c) seven levels* [7]

FC inverter has a modular structure and it is used widely in high frequency applications like the medium voltage traction systems. In addition, in the FC inverter both real and reactive power flow can be controlled and the large number of capacitors enable the inverter to ride through power outages and deep voltage sags. Similar to NPC inverters, for high number of levels topologies, the control process will be complicated, the switching utilization and inverter efficiency are poor in real power transmission applications, the inverter cost will be very expensive and its size will be bulky [1], [2], and [23].

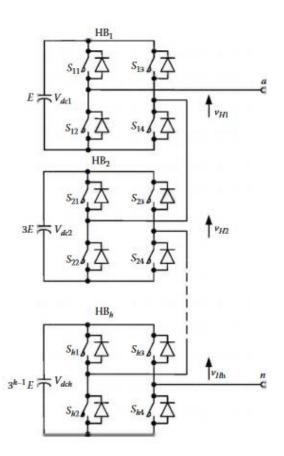

#### 3.1.2 Hybrid Multi-Level Voltage Source Inverter

Nowadays, researchers focus their studies on proposing new hybrid inverters to overcome problems of the Multi-Level inverters related to the relative high number of the switches in some topologies, control complexity for high level inverters, DC isolated power supplies and the capacitor voltage regulations. Mainly, those Hybrid Multi-Level inverters are derived from the classical topologies of the Multi-Level Inverters mentioned previously. That is to meet the high grid code standards and the power quality issues in an economical way. There are many new topologies that are presented in literature, each has its own structure, applications, advantages and drawbacks. A review of various topologies will be listed, studied and analyzed. However, just a few of them will be considered and simulated using MATLAB/Simulink.

Hybrid Multi-Level inverters that will be presented and discussed are:

- 1- Mixed-Level Hybrid Multi-Level Inverters

- 2- Asymmetric Binary Hybrid Multi-Level Inverters (BHMLI)

- 3- Asymmetric Trinary Hybrid Multi-Level Inverters (THMLI)

- 4- Hybrid Multi-Level Inverter Using Switched Capacitor Units

- 5- Multi-Level DC-Link Inverter

- 6- Hybrid Multicell Converter Topology and Modulation

- 7- Hybrid Multi-Level Converter with Distinct Series Connected Cells [8][11].

- 8- Hybrid Asymmetric Multi-Level Inverter for Competitive Medium-Voltage Industrial Drives [28].

- 9- New Hybrid Asymmetrical H-bridge Multi-Level Inverter[29].

- 10-Hybrid Multi-Level Inverter with Single DC Source [30].

However, there are many other topologies such as:

- 1- New Symmetrical Hybrid Multi-Level DC-AC Converters

- 2- Hybrid-Clamped Multi-Level-Inverter Topologies

- 3- Hybrid Multi-Level Inverter based on main inverter and conditioning inverter [11][31].

Kala and Arora, in [2], divided the Hybrid Multi-Level Inverter into three main categories:

1- Reduced Components Count (RCC) topologies with H-bridge:

These types of Hybrid Multi-Level Inverters are mainly used in the Low Voltage (LV) and PV applications. They also have the separate polarity generation and level generation blocks. This category includes:

- a- Developed Cascaded Multi-Level Inverter (DCMLI)

- b- Cascaded Sub-Multi-Level Inverter (CSMLI)

- c- Multi-Level DC Link Inverter (MLDCLI)

- d- Hybrid Multi-Cell Converter (HMC)

- e- Series Diode Clamped H-bridge Multi-Level Inverter (SDCHB MLI)

- f- Switched Series/Parallel Sources Multi-Level Inverter (SSPS MLI)

- 2- Reduced Components Count (RCC) topologies without H-bridge:

This type of Hybrid Multi-Level Inverters is mainly considered for medium voltage (MV) applications. They consist of series connected unit cells with bipolar waveform generation capability. This category includes:

- a- Cascaded Basic Blocks Multi-Level Inverter (CB MLI)

- b- Cascaded Modified H-bridge Multi-Level Inverter (CMB MLI)

- c- Chain Cell Multi-Level Inverter (CC MLI)

- d- Cross Connected Sources Based Multi-Level Inverter (CCS MLI)

- e- Level Doubling Network Based Cascaded MLI (LDNC MLI)

- f- Switched Capacitor Cell Hybrid Multi-Level Inverter (SCH MLI)

- 3- Miscellaneous Hybrid Multi-Level Inverters

Some are mainly intended for medium and high voltage applications. Others utilize variable ratio transformers for producing a greater number of voltage levels while boosting the LV supply obtained from standalone PV arrays and fuel cells. These include:

- a- Switched Ladder Multi-Level Inverter (SL MLI)

- b- Asymmetrical Transistor Clamped H-bridge MLI (ATCHB MLI)

- c- Nested Neutral Point Clamped (NNPC) Converter

- d- Active Neutral Point Clamped (ANPC) Converter

- e- Pulse Width Modulation Based Multi-Level Inverter (PWM MLI)

#### **3.2 Current Source Inverters**

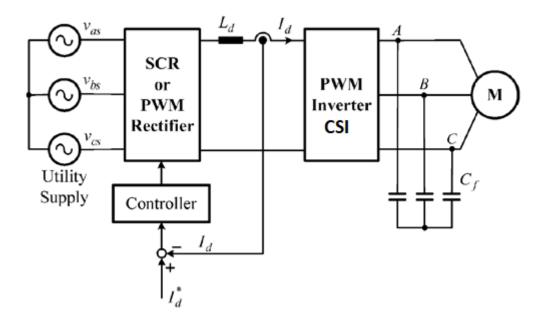

The main objective of using Current Source Inverters (CSIs) is to generate an AC output waveform from a current DC source. The output current has a controllable magnitude, frequency and phase shift. It is common to use a capacitive filter with inductive load application. Since the DC bus is a current source type, it cannot be opened; therefore, at least there must be one switch closed at each moment of time. Thus, overlap periods are required. Although Current Source Inverters are less popular than the voltage source inverters, they have more advantages. They are widely used in High Voltage motor drive applications, and they are highly recommended in application were boosting capabilities are required [32]–[34].

Current Source Inverters are classified into the following types:

- 1- Pulse Width Modulated Current Source Inverters (PWM CSIs)

- 2- Parallel Current Source Inverters (PCSIs)

- 3- Load-Commutated Current Source Inverters (LC CSIs)

- 4- Boost Type Current Source Inverters (BT CSIs)

- 5- LC Current Source Inverters (CSIs)

- 6- Multi-Level Current Source Inverters (ML CSIs)

- 7- Hybrid Multi-Level Current Source Inverters (HML CSIs)

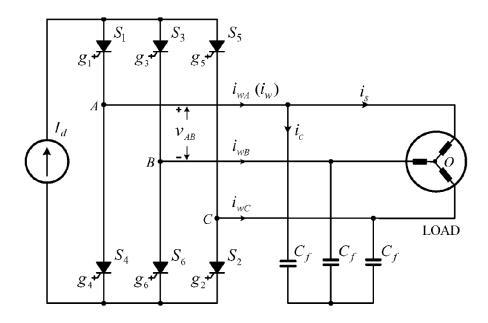

#### 3.2.1 PWM Current Source Inverter

It consists of six switches divided as couples into three legs, the reason for naming it in some references as a three-phase full bridge Current Source Inverter. In some cases of MV/HV applications each switch can be replaced by two or more switches in order to raise the inverter's power capabilities [23]. All switches in the PWM CSI are identical and have a reverse voltage blocking capability. Fig. 3-7 shows the topology of the PWM CSI.

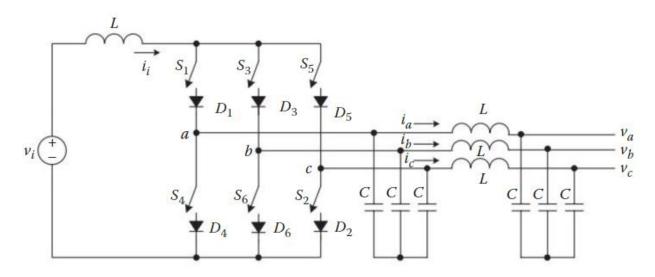

Fig. 3-7 A PWM Current Source Inverter [23]

In general, the Current Source Inverter requires a capacitive load at its output (capacitors) to assist the commutation of the switches. Besides, the output capacitors act as harmonics' filter that improves the load current and voltage waveforms. The DC current source can be achieved from a closed loop-controlled PWM current source rectifier, and it can be smoother and more continuous using a DC choke in series with the voltage source, as shown in Fig. 4-8.

Fig. 3-8 Realization of the DC current source in PWM CSI [23]

Pulse Width Modulated Current Source Inverter has the following characteristics:

- 1- Simple structure: switches with reverse blocking capability are used, thus they do not require the antiparallel freewheeling diodes.

- 2- Motor friendly waveforms: the output waveforms of the PWM CSI are much closed to the sinusoidal shape. That is because the high dv/dt problem existing in the Voltage Source Inverters VSIs does not exist in CSIs.

- 3- Reliable short-circuit protection: since the DC choke in the input side limits the rise rate of the short circuit current, which gives more time for protection devices to trip accordingly.

- 4- Limited dynamic performance: since the DC current cannot be changed instantaneously during transient (drawback).

#### 3.2.2 Parallel Current Source Inverters

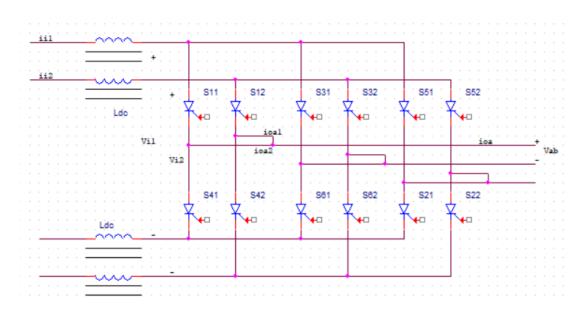

For high power applications, a parallel topology of the PWM CSI can be used. Also, series switches instead of each individual switch can be used, as shown in Fig. 3-9. Both inverters are sharing the same output capacitor filter, but each one has its own series DC choke [23], [35], and [36].

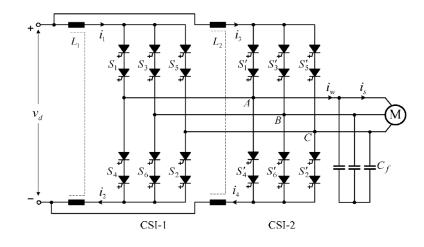

Fig. 3-9 Parallel CSIs for high power applications [23]

Actually, this schematic has some drawbacks regarding the balance of the DC currents [36]; (a) unequal on-state voltages of the switches, that affects the balance of the DC current and needs more advanced control techniques (b) Any time variation occurring between the gate signals of both inverters' switches will affect the DC current balance during both steady state and transients modes (c) tolerance between DC chokes for each inverter. Nonetheless, Space Vector Modulation (SVM) may be used to solve the problem of the DC current balance [35], [36].

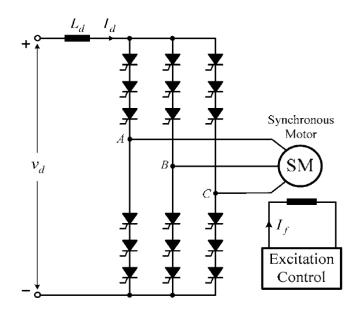

#### 3.2.3 Load-Commutated Current Source Inverter (LC CSI)

It is a very well-known Current Source Inverter topology [37]. It has a relatively simple structure and capable of very high-power levels. Besides, its manufacturing cost is low since it depends on the SCR switches in its structure. A DC choke is used in the input side to smooth the DC current. Fig. 3-10 shows a Load Commutated Current Source Inverter for a synchronous motor drive.

Fig. 3-10 LCI for SM drive [23]

SCR switches are used in the LC CSI, instead of the Gate Commutated Thyristor (GCT) switches that are used in the PWM CSI. That means, they are not capable to turn off by themselves. They can be naturally commutated by the load voltage with a leading power factor. That justifies why it is used extensively in the synchronous motor drives [23]. Since it's easy to operate the SM at a leading power factor by adjusting the excitation current. A concern appears at the low speeds of the motor, where the induced EMF value is not enough to commutate the SCRs, in this case the commutation is done using front-end SCR rectifiers [37]. That causes a low dynamic performance of the LC CSI. Besides that, the power losses in the motor are large due to the large amounts of harmonics in the stator current [38].

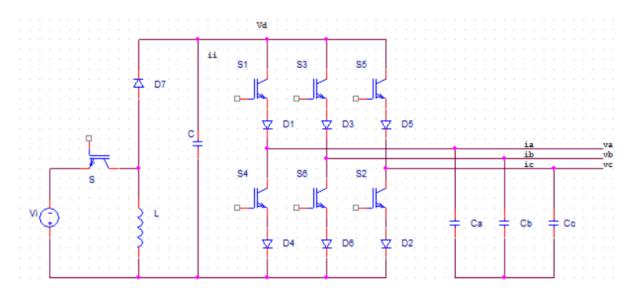

### 3.2.4 Boost-Type CSI

This type of Current Source Inverter is divided into two categories: a negative polarity and a positive polarity Boost Current Source Inverters [7].

### 3.2.4.1 Negative Polarity Boost-type CSI

It is proposed to be used in the photovoltaic systems to improve the power quality, reduce the current harmonics and decrease the switching frequency. Besides, this topology can complete the maximum power point tracking [39][40]. Fig. 3-11 shows the inverter topology.

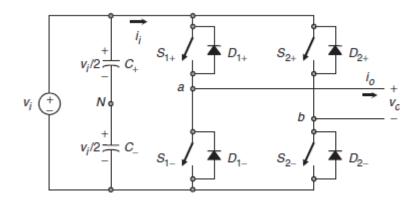

Fig. 3-11 Negative Polarity Boost-Type CSI

It's noticed from Fig. 3-11 that; the input voltage is a negative polarity source. Components  $v_i$ , L, C and the switch "s" form a DC-DC boost converter. The voltage  $v_d$  can be more or equal to the input voltage. Actually, the circuit from  $v_d$  to  $(v_a, v_b, v_c)$  is a voltage source inverter.

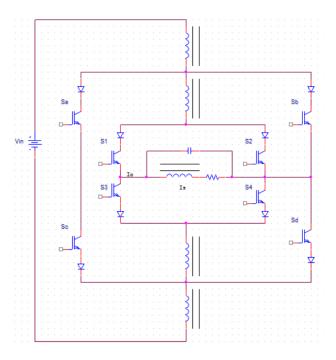

### 3.2.4.2 Positive Polarity Boost-type CSI

It doesn't differ too much from the topology of the negative polarity CSI. Fig. 3-12 shows the topology for the positive polarity boost-type CSI. Components  $v_i$ , L, C and the switch "s" form a DC-DC boost converter. The voltage  $v_d$  can be more or equal to the input voltage. Actually, the circuit from  $v_d$  to  $(v_a, v_b, v_c)$  is a Voltage Source Inverter [7].

Fig. 3-12 Positive Polarity Boost-Type CSI

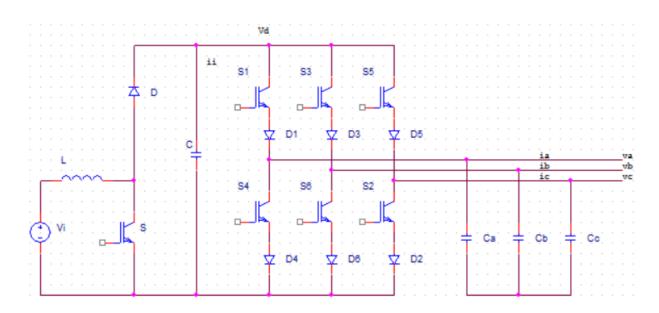

### 3.2.5 LC CSI

This topology is derived from the full bridge Current Source Inverter. The LC filter has boosting characteristics, which means that the output voltage can be higher than the input voltage. Fig. 3-13 shows the structure of the LC CSI.

Fig. 3-13 LC Current Source Inverter

Many advanced control processes were proposed for the LC CSI [41][42]. Most of these control processes depend on the Space Vector Modulation (SVM).

### 3.2.6 Multi-Level Current Source Inverters (MCSIs)

Using a series inductor with the voltage source to get the required Current Source in the Current Source Inverters was one of the most important reasons behind the low popularity of them. They have higher conduction losses and so, a low efficiency inverter compared to capacitors used in the voltage source inverters. However, this problem is to be solved following the development of Superconducting Magnetic Energy Storage (SMES) technologies. In addition, the need for the series blocking individual diode with the switching device has been eliminated by the recently produced Reverse Blocking Insulated Gate Bipolar Transistor (RB-IGBT). That makes the use of Current Source Inverters more usable in high power applications [43].

Many Multi-Level Current Source Inverter topologies are proposed in literature. Each topology has its own applications, advantages and drawbacks. Here are the most CSIs that have been discussed and studied by researchers in the last few years:

- 1- Dual PWM CSI [1], [44]

- 2- Embedded Multi-Level CSI [34]

- 3- Two-Stage Multi-Level CSI [34]

- 4- Cascaded Multi-Level CSI [43]

- 5- Single Rating Inductor Multi-Level CSI [45]

- 6- Back to Back Multi-Level CSI [46], [47]

- 7- Reduced Count Switch Multi-Level CSI [48]

- 8- Parallel Inductor Multi-Level CSI [49]

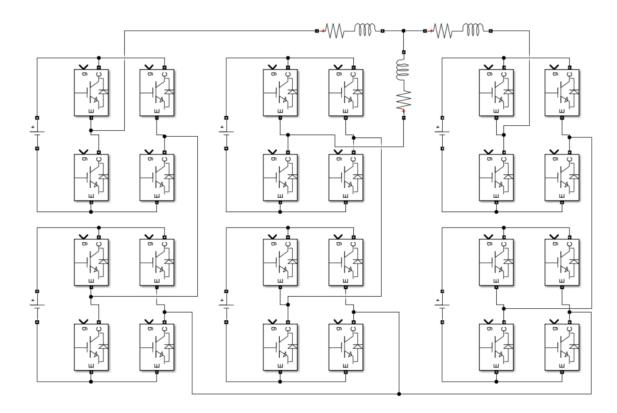

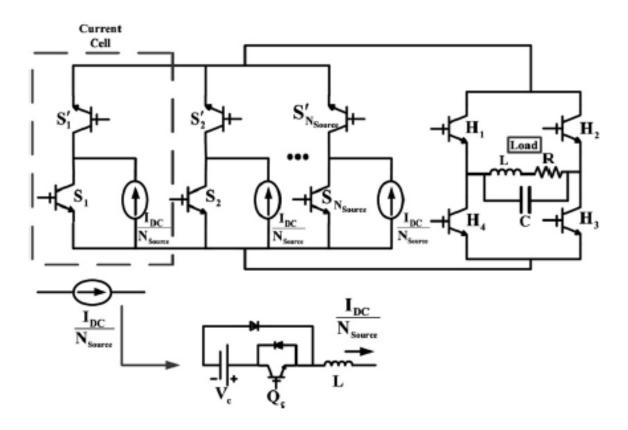

### 3.2.6.1 Dual PWM Current Source Inverter

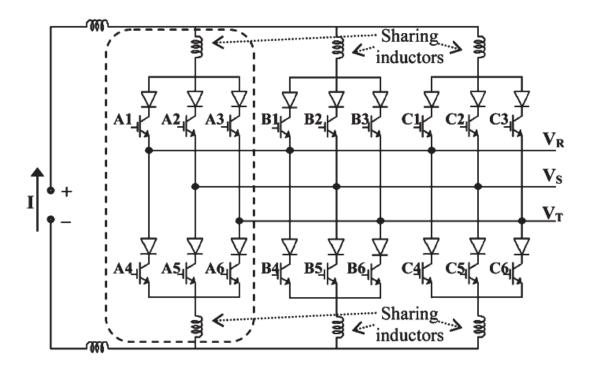

In some references, it is called parallel PWM Current Source Inverter [1]. It is formed by paralleling two or more standard PWM Current Source Inverters. Fig. 3-14 shows the three-level topology of this type of inverters. The main concept of this inverter is to equally share the AC current  $i_o^{abc}$  among the standard topologies  $\left(\frac{i_o^{abc}}{o}\right)_2 = i_{o1}^{abc} = i_{o2}^{abc}$ . That means that, both current sources must be equal  $i_{i1} = i_{i2}$ . It can be achieved by using two separate DC current sources or by properly controlling the gate signals of switches. Actually, this is the main challenge in this type of inverters, and many solution were presented to solve this problem [1]. It is common to use the sinusoidal pulse width modulation technique for the dual Multi-Level Current Source Inverters.

Fig. 3-14 Three-level Dual PWM Current Source Inverter

# 3.2.6.2 Embedded Multi-Level CSI

It is one of the simplest topologies for the Multi-Level Current Source Inverters. It can be generalized easily for any number of levels. In [50], two switching methods were introduced to control the gate signals of the switches, symmetrically and asymmetrically. Fig 3-15 shows the 5-level topology for the embedded current source Multi-Level Inverter.

Fig. 3-15 Five-level Embedded Multi-Level CSI

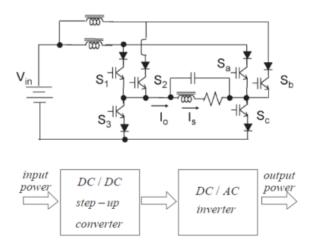

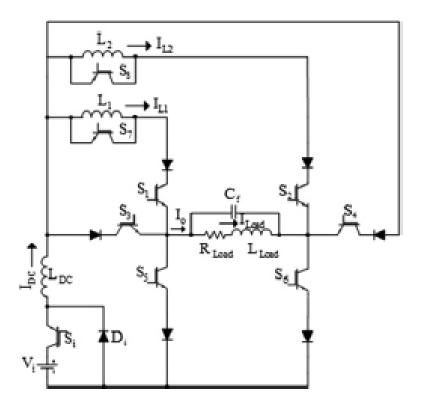

### 3.2.6.3 Two-Stage Multi-Level CSI

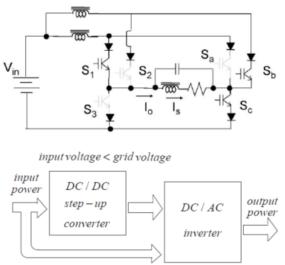

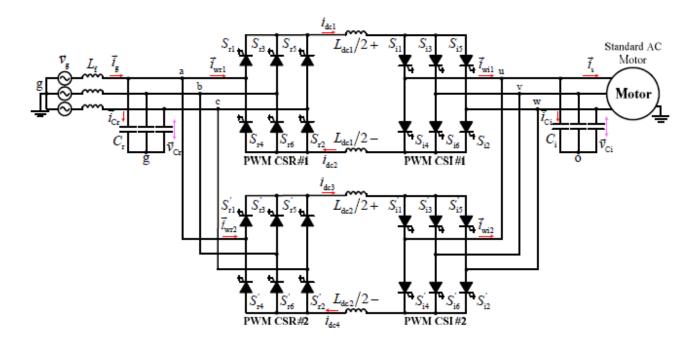

Different topologies that have mini differences were proposed for the Two-Stage Current Source Multi-Level Inverters [34], [51]. Basically, all proposed topologies consist of two different stages, the first one is a power boosting stage (boost converter), whilst the other is a DC to AC conversion stage (Current Source Inverter), as shown in Fig 3-16. Actually, the two-stage power conversion system means that, the power will be transmitted twice, so the power losses in this case is a main concern. In some cases where the DC input is more than the AC output voltage, the pre-stage is not necessary to be used. That may improve the efficiency of the system and reduce power stress of the boosting stage [51]. Fig 3-17 shows the semi-two-stage Multi-Level based on the last idea.

Fig. 3-16 Two-stage Multi-Level CSI [34]

input voltage > gridvoltage

Fig. 3-17 Semi-two-stages Multi-Level [34]

### 3.2.6.4 Cascaded Multi-Level CSI